Memories – Materials, Devices, Circuit and Systems (存储器 - 材料、设备、电路和系统)期刊最近发表了一篇文章,名为:Improvement of memory performance of 3D NAND flash memory with retrograde channel doping(通过逆行通道掺杂改善3D NAND闪存的内存性能)。

摘要:“本文研究了逆行通道掺杂对基于3D无结点NAND的闪存的可靠性和性能的影响。具体来说,我们研究了程序特性,数据保留能力无结NAND闪存,半间距范围从35nm到12nm。根据我们的分析,我们强调逆行通道掺杂方法不仅可以提高SCE,还可以提高3D无结NAND闪存的程序速度和数据控制时间,而不会改变基于电荷撷的闪存中的氧化物堆栈。

1. 简介

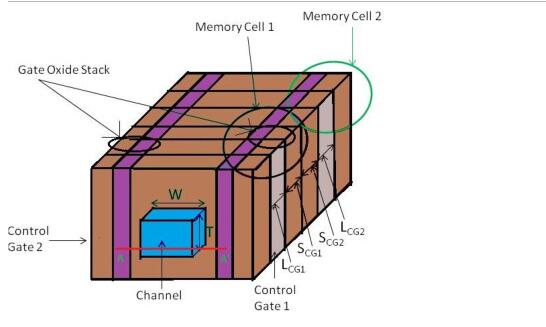

闪存是现代手持设备的关键组件之一。这些器件的小尺寸要求引发了闪存向中1x-nm一代的扩展,这在实践中带来了严峻的挑战[1]。较低的栅极耦合比、电池间干扰、应力感应漏电流(SILC)等。严重影响典型的基于浮栅(FG)的闪存缩放[2],[3]。相比之下,基于电荷撷取(CT)的闪存最近因其MOSFET兼容晶圆厂制造工艺,较少的电压功能,抗外部电荷损耗,紧凑的堆叠和缩放能力而引起了重大的研究兴趣[4],[5],[6]。因此,与FG闪存相比,CT闪存是实现更大缩放限制[7]的潜在候选者。最近,由于3D NAND闪存的发展,基于CT的闪存市场出现了巨大的增长,例如位成本可扩展存储器[8],[9],垂直堆叠阵列晶体管存储器[10]和太比特单元阵列晶体管存储器[1],[11]。 .在这里,值得一提的是,基于3D NAND的闪存比2-D闪存运行得更快,因为大量芯片密集地封装在一起。此外,基于 3D NAND 的闪存比 2-D 闪存提高了磨损寿命。因此,基于3D NAND的闪存每KB数据具有较小的误码率(BER),并且对纠错码的鲁棒性要求较低。此外,基于该制造,文献中提出了几种3D NAND闪存结构,即栅极堆叠和通道堆叠。请注意,与栅极堆叠式3D NAND闪存相比,由水平通道堆叠的通道堆叠在间距缩放、通道材料的偏好以及大量堆叠层的读取电流剥夺方面似乎更具吸引力[12]。因此,在本文中,我们主要关注基于通道堆叠的3D NAND闪存。

全文地址:https://www.sciencedirect.com/science/article/pii/S2773064623000087