深度学习在2016年持续成为业界热门话题。而在即将来临的2017年里,专家们称人工智能社区对高性能、高效的深层神经网络“推理”引擎的需求将迅猛增加。

时下的深度学习系统主要是在定义网络、训练大数据集时利用强大的计算资源,而在达到目标时则需访问大型计算机系统。

不幸的是,要在嵌入式系统(如汽车、无人驾驶飞机和物联网设备)上有效地实现类似的学习并不容易,原因是嵌入式系统的处理能力、内存和带宽通常是有限的。

因此,深度神经网络(DNN)使得创新技术大有可能在端点设备上发挥其威力。

Movidius首席执行官Remmi El-Ouazzane 几个月前告诉记者,“在网络边缘上部署人工智能是大趋势。”

Marc Duranton

Marc Duranton是CEA(Commissariat à l'Énergie Atomique法国能源委员会)的架构、集成电路设计和嵌入式软件部的院士。记者最近采访他时问到推动人工智能的动力是什么。他提到三个因素——“安全、隐私和经济”,他认为这三个因素将推动业界在端节点处理数据。Duranton觉得 “尽可能早地将数据转换成信息” 的需求在不断增长。

他表示,自主汽车就是个例子。如果目标是安全的话,自主功能就不应该依赖总是有连接的网络。比如一个老人在家里摔倒了,这一事件应该在本地检测和识别。Duranton表示,由于隐私的原因,这一点颇为重要的。他还表示,家里安装的用于触发警报的10个相机将收集大量图片,不发送这些图片可以减少“功率、成本和数据的大小”。

竞赛开始了

从许多方面来看,芯片厂商已经充分认识到了业界对更好的推理引擎的需求在日益增长。

诸如Movidus(配备了Myriad 2)、Mobileye(EyeQ 4 & 5)和英伟达(Drive PX)的半导体供应商都在竞相开发超低功率、具更好的性能的硬件加速器,以用于嵌入式系统上实现更好的学习。

Duranton指,单片机系统(SoC)方面的研究表明,推理引擎已经在后移动时代成为许多半导体公司的“新目标”。

谷歌今年早些时候发布了张量处理元(TPU),这标志着工程社区在机器学习芯片方面渴望创新,是个转折点。

搜索巨头谷歌在发布TPU时称,TPU产品比 “商业FGPA和GPU在每瓦特性能上高一个数量级 “。谷歌还透露,击败人类围棋冠军的AlphaGo系统也用了这些加速器。但谷歌未公开讨论过TPU结构的细节,谷歌亦不会在商业市场出售TPU。

许多SoC设计师认为,谷歌之举印证了机器学习需要自定义架构的说法。而在他们试图设计自定义机器学习芯片时,他们很好奇TPU的架构是什么样子。更重要的一点是,他们想知道业界是不是已经有基准测试工具可以衡量深层神经网络在不同类型硬件上的性能。

工具来了

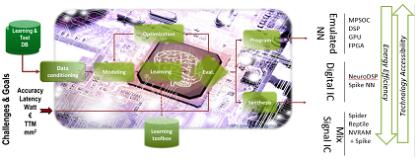

CEA称已经准备就绪,将探索各种不同硬件结构的推理引擎。CEA开发了一个软件框架,名为N2D2,设计师利用N2D2能够探索和生成DNN结构。Duranton表示, “我们开发这个工具的目的就是为了选择正确的DNN硬件。“他还承诺,N2D2在2017年第1季度将开源提供给公众使用。

新工具N2D2的关键是,N2D2比较硬件时不仅仅是基于识别精度。N2D2还将比较硬件的“处理时间、硬件成本和能源消耗”。Duranton表示,“这一点至关重要,因为不同的深度学习应用在各种硬件实现中用的参数可能不同。

N2D2的工作方式(来源:CEA)

N2D2提供了各种市场上有售的商业硬件的基准测试,包括多内核/博内核CPU、GPU和FPGA。

边缘计算遇到的障碍

CEA是个研究机构,一直在研究如何最好地利用深层神经网络在边缘计算中的使用。在被问到DNN在边缘计算遇到的障碍是什么时,Duranton表示,很明显,“浮点” 服务器解决方案是不能用的,因为“功率、大小和延迟的约束”。 他还表示,其他局限性包括:“许多MAC、带宽和片上内存大小”。

即是说“整数而不是浮点”是我们需要考虑的第一件事。还要考虑别的吗?

Duranton认为,另外,还可以在专业架构里使用新编码,如“高峰编码”(Spike coding)。

CED研究人员对神经网络的属性进行了研究,他们发现这些属性本质上可以容许一些计算误差的存在。他们因此确定,神经网络适合”近似计算“。

如果这样的话,我们就不一定需要用二进制编码。Duranton表示,这是个好消息,因为如高峰编码之类时间编码在边缘上能得到更节能的结果。

高峰编码有其吸引力,因为经高峰编码过的(基于事件的)系统可以显示神经系统的数据如何被编码。而且,基于事件的编码可以兼容专用传感器和预处理。

再者,使用与神经系统所用的码类似的码将有利于模拟和数字的混合实现,研究人员因此可以构建一个更小的、能量消耗也更小的硬件加速器。

还有一些其它因素可以帮助加快DNN在边缘计算中的使用。

例如,CEA正在考虑微调神经网络结构的潜在需要,并将其用于边缘计算。Duranton指,“人们开始谈 “SqueezeNet”的使用,不再谈AlexNet。他解释说,有报告说SqueezeNet可以达到AlexNet层面的准确性,但用的参数只有1/50。在边缘计算中需要的就是这种简化,在拓扑方面和减少MAC数量方面都有需要。

在Duranton看来,目标是将 “经典”DNN自动转换到“嵌入式”网络。

P-神经元(P-Neuro)临时芯片

CEA的目标是开发神经形态电路。CEA研究所认为这种芯片电路是“对深度学习的有效补充,可以在接近传感器的数据里提取信息” 。

在实现该目标前,CEA觉得先要采取几个临时措施。像N2D2的开发工具对于芯片设计者十分重要,可用于开发定制的“每瓦特高TOPS(tera operations per second,每秒Tera操作)性能的DNN”解决方案。

此外,想在边缘计算中利用DNN的开发者可以用真正的硬件做实验。为此,CEA提供一款超低功耗的可编程加速器,名为P-Neuro。

目前的P-Neuro神经网络处理单元基于FPGA。据Duranton说,CEA以后会将FPGA转成ASIC。

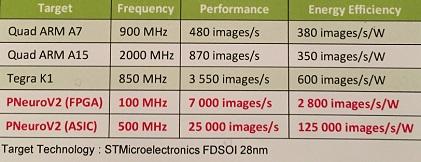

试验演示:P-Neuro与嵌入式CPU的比较

Duranton在实验室演示了基于FPGA的P-Neuro卷积神经网络用于人脸检测的应用程序。演示将P-Neuro与嵌入式CPU(Raspberry Pi上的四核ARM;运行Android的三星Exynos)进行比较,运行的都是相同的嵌入CNN应用程序,任务是从18000张的图片数据库里做 “人脸提取”。

演示 (如上图所示) 结果显示,P-Neuro的速度性能是每秒6942张图片,能源效率每瓦2776张照片。

P-Neuro栈与嵌入式CPU、GPU的对比(来源:CEA)

与嵌入式GPU(Tegra K1)相比,频率为100 Mhz的基于FPGA的P-Neuro的运行速度要快2倍,节能达4到5倍。

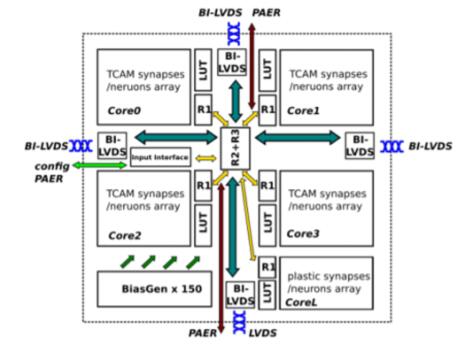

P-Neuro建立于集群SIMD架构上,特点是内存层次结构和互连得到优化。

P-Neuro框图(来源:CEA)

欧盟项目

Duranton强调指出,对于CEA研究人员而言,P-Neuro只是个”短期芯片”。P-Neuro的建立用的是使用二进制编码的完整CMOS元件。CEA研究小组也在研究使用高峰编码的完整CMOS元件。

而为了充分利用先进的元件解决密度和功率上的问题,CEA团队必须设定更高的目标。

在采访期间,CEA-Leti纳米电子学技术营销和策略主管Carlo Reita表示,关键是要在设计专用组件的物理实现时利用先进的硅元件和记忆技术。Reita表示,一个方法是用传统的整体式三维集成,用上CEA-Leti的CoolCube。另一个方法是用电阻式RAM作突触元素。诸如FD-SOI等先进元件技术和纳米线技术也将发挥其作用。

与此同时,欧盟推出了欧盟地平线2020计划,其中一个项目的目标是“制造能实现神经形态架构的芯片,以支持先进的机器学习和基于高峰编码的学习机制”。

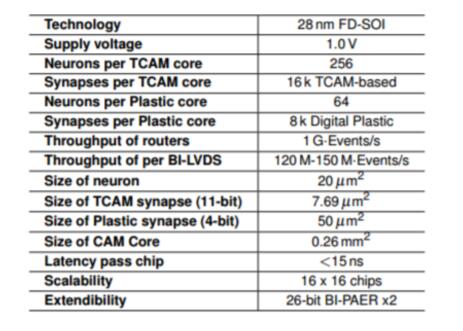

神经形态处理器

该项目名为NeuRAM3。NeuRAM3称自己的芯片将具有“超低能耗、可伸缩和高度可配置的神经结构“的特点。其目标是提供“针对一些选定的应用程序比传统的数字解决方案优于50倍的功耗”。

神经形态处理器(来源:Giacomo Indiveri教授)

神经形态处理器基本规范 (来源:Giacomo Indiveri教授)

Reita表示,CEA深度参与了NeuRAM3项目。CEA自己的研究目标与NeuRAM3项目的目标一致,这些目标包括开发在FD-SOI上单片集成的3D技术及集成RRAM突触元素的使用。

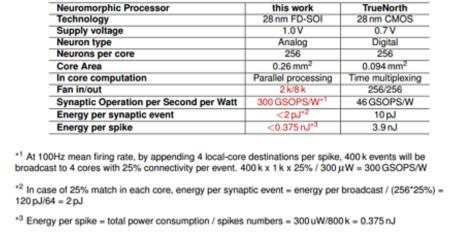

Reita解释说,NeuRAM3项目研究出新的混合信号多核神经形态元件,与IBM的名为TrueNorth的人脑式元件比较,NeuRAM3的神经形态元件的功耗显著降低了。

NeuRAM3的神经形态元件与IBM的TrueNorth的比较(来源:NeuRAM3)

NeuRAM3项目的其他参与者包括:IMEC、IBM(苏黎世)、ST Microelectronics、CNR(意大利国家研究委员会)、IMSE(El Instituto de Microelectrónica de Sevilla in Spain,西班牙塞维纳微电子研究院)、苏黎世大学和德国雅各布斯大学。