中国存储网消息,近日Kioxia 恺侠公司宣布开发高度堆叠的氧化物-半导体通道晶体管,将实现高密度、低功耗三维DRAM的实际应用。

三维OCTRAM单元结构

该技术于12月10日在美国加利福尼亚州旧金山举行的IEEE国际电子器件会议(IEDM)上进行了展示,有望在包括人工智能服务器和物联网组件在内的广泛应用中降低功耗。

在人工智能时代,对容量更大、功耗更低、能够处理大量数据的DRAM需求日益增长。传统的DRAM技术正接近存储单元尺寸扩展的物理极限,促使对存储单元三维叠加的研究以提供额外容量。在堆叠存储单元中,使用单晶硅作为晶体管通道材料,如传统DRAM使用,这会推高制造成本,且刷新存储单元所需的功率与存储容量成正比增加。

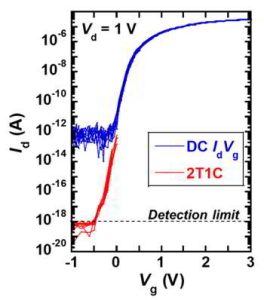

氧化物-半导体水平晶体管的电气特性

在去年的IEDM大会上,恺侠宣布开发了使用由氧化物半导体构成的垂直晶体管的氧化物-半导体通道晶体管DRAM(OCTRAM)技术。在今年的展示中,我们展示了高度可堆叠氧化物半导体通道晶体管技术,实现OCTRAM的三维堆叠,验证了8层晶体管的工作原理 。

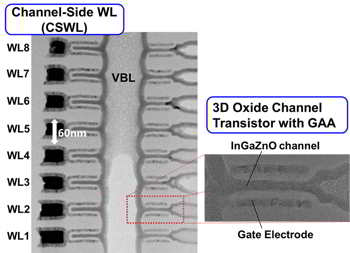

8层氧化物半导体水平晶体管的横截面TEM图像

这项新技术将成熟的氧化硅和氮化硅薄膜叠加,并用氧化物半导体(InGaZnO)替代氮化硅区域,同时形成水平堆叠的垂直晶体管层。Kioxia还引入了一种新型三维存储单元结构,能够垂直音高的扩展。这些制造工艺和结构预计将克服实现存储单元三维堆叠的成本挑战。

此外,由于氧化物半导体的低离流特性,预计刷新功率可以降低。Kioxia已展示了替代工艺形成的水平晶体管的高导通(超过30μA)和超低离流(低于1aA,10^-18A)的能力。此外,公司成功制造了一个8层水平晶体管堆叠,并确认晶体管在该结构内的正常工作。

公司将继续对该技术进行研发,以实现3D DRAM在实际应用中的应用。