半导体联盟消息,针对5G通讯毫米波(mm-Wave)开发趋势,AiP(Antenna in Package)封装技术将成为实现手机终端装置的发展关键。随着高通(Qualcomm)于2018年7月推出的AiP模组(QTM052及525)陆续问世后,各家厂商对此无不摩拳擦掌,争相投入相关模组的技术研制上;其中半导体制造龙头台积电及封测大厂日月光投控,对此最为积极。

日月光投控对于AiP封装技术之演进,凭借日月光及矽品对于相关封装的长期研发,以及旗下环旭电子增设天线测试实验室的积极投入态度,为此将进一步扩充5G毫米波之发展进程。

高通推出AiP模组后,制造龙头台积电与封测大厂日月光等皆已跃跃欲试

面对5G通讯毫米波逐步发展之际,加上高通已推出的AiP模组产品,各家IDM厂、Fabless厂、制造及封测代工厂商,对此无不跃跃欲试,试图加速开发相关产品,从而应付为数庞大的射频前端市场及5G应用商机。

为了实现AiP封装制造技术,现行除了已开发出InFO-AiP封装技术的半导体制造龙头台积电外,其他封测厂商(如日月光、Amkor、江苏长电及矽品等)也有相应的布局动作,并采取默默耕耘的发展态势,以求提供后续5G通讯毫米波之市场需要。

其中,若以日月光及矽品发展动态为例,现阶段AiP封装技术主要采用RFIC于底层的设计架构,相较于台积电在内层及其他厂商于上层之结构,整体于制作成本上,相较其他产品将更具吸引力。

日月光与台积电于AiP封装技术差异,使产品特性及成本已成为选择难题

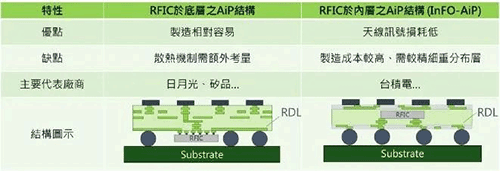

针对现行AiP封装技术,进一步比较于台积电内层式之InFO-AiP构造,以及日月光与矽品于底层式的AiP结构差异,可发现RFIC的摆放位置,将是决定模组产品之性能表现(天线讯号损耗、散热机制)及成本高低(制造良率及难易度)的重要指标。

图:RFIC于不同位置之AiP结构比较表(Source:拓墣产业研究院整理)

其中,以日月光与矽品开发之AiP封装架构为探讨主题时,当RFIC放置于底层结构中,此结构确实能有效降低封装成本,并且对于开发流程上也十分有利;由于封测厂商于相关制作流程中,可独立开发重分布层(RDL),并搭配上单独封装好的RFIC,最后再将二者结合于一体,以完成AiP所需的架构。

如此之设计理念,对于管控封装成本而言,已起到节省工序作用;然而却也衍生出另一个难题,“如何将底层的RFIC在运作时产生之热源有效导引出来”,这将是后续亟需克服的关键要务之一。

另一方面,台积电开发的InFO-AiP封装技术,由于运用本身擅长的线宽微缩技术,当RFIC于元件制造完成后,随之进行一系列的后段封装程序;也在此时延伸原有的通讯元件金属线路,将使重分布层得以连结RFIC并导引至天线端,从而达到降低天线端讯号衰弱之效果。

整体而言,虽然日月光及矽品的AiP结构可有效降低成本,但散热机制仍需额外考量,且台积电的InFO-AiP能成功增进产品效能,然而整体封测制造成本却依旧偏高。

由此可见,AiP封装技术于产品特性及成本表现之因素中,已成为一项选择难题,考验未来客户在产品设计及应用需求上应该如何取舍。