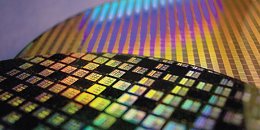

台积电3日宣布,在开放创新平台 (Open Innovation Platform,OIP) 之下推出5纳米设计架构的完整版本。台积电方面表示,目前5纳米制程经完成了5纳米工艺的基础设施设计,进入试产阶段,能够提供芯片设计业者全新等级的效能及功耗最佳化解决方案。5纳米能够提供7纳米工艺1.8倍的逻辑密度,速度增快15%,在此制程架构之下也产生出优异的SRAM及类比面积缩减。5纳米制程享有极紫外光微影技术所提供的制程简化效益,同时也在良率学习上展现了卓越的进展。

事实上,之前台积电总裁魏哲家就曾经表示,2019年上半年将流片5纳米制程,2020年上半年则将正式量产5纳米制程。目前包括苹果A12等处理器皆采用台积电7纳米制程晶片,但首代7纳米制程采用DUV技术,已经无法满足更先进制程技术需求,因此台积电狂吃18台EUV光刻机数量,除了加速EUV技术7纳米加强版制程量产外,也为往后5纳米制程技术扎根,除拥有多家高阶手机晶片代工肥单外,未来5G及AI主流市场订单也可望到手。

另据相关报道,三星虽然早在2018年10月份就已经宣布量产7纳米EUV制程,但实际情况并非如此。因为就连三星自己的Exynos 9820处理器都没用上7纳米EUV制程,这是因为三星的7纳米工厂过去一直都没完成。直到日前,三星提交的报告显示,他们投资13亿美元的华城生产线已经完成建设工作,三星的7纳米EUV制程现在才算真正进入量产。三星7纳米EUV制程的大量生产,预计在2020年底前达成。

事实上,在联电、格罗方德相继退出10nm以下制程市场,以及英特尔2018年陷入产能不足的窘境后,三星被认为是晶圆代工龙头台积电近2年的唯一对手,与其一同竞争英伟达、高通等有7nm EUV技术需求的客户。三星目标在2023年前拿下25%的市场占有率。但三星的目标能否实现,有待今后市场验证。